春先に火を入れたきりになっていたFPGAボード「Digilent Arty」ですが、普段使っているノートPCのRAMを最近16GBに拡張したので、ようやく開発ツール「Vivado」を動かしてみました。

やはりというか起動するとPCのメモリ消費が12GBくらいになりました。

もしRAMが8GBだったら辛そうです。

ちなみにArtyはVivadoの初期インストール時にはボードのデータが入っておらず、ボード一覧からArtyを選択できません。

Digilentからボード設定ファイルをダウンロードして、Vivadoのフォルダにコピーする必要があります。

Vivadoプロジェクト作成時のボード選択 – 石丸技術士事務所 FPGAと論理設計

本命としてはRISC-Vを動かしてみたいのですが、XilinxのツールはWebpack ISEしか使ったことがなかったので、とりあえず以下のチュートリアルをやってみました。

Vivadoでmicroblaze – fpgafpga ページ!

今のVivadoよりもバージョンが古いので、最新のVivadoとは画面が細かいところで若干違いはありますが、STEP BY STEPで書かれているので、概ねこの通りにやれば大丈夫です。

ノートPCとはいえCore i7なのですが、MicroBlazeがビルドできるまで結構時間がかかりました。

これでMicroBlazeの上でHello worldとLチカができてVivadoの雰囲気が分かってきたので、次はRISC-Vを動かしてみました。

RISC-Vはソースからビルドするのは大変そうですが、Artyの場合はSiFive製の評価用ビットストリームがあるので、これを書き込めば済みます。

SiFive Developers — Evaluate FPGA Bitstreams

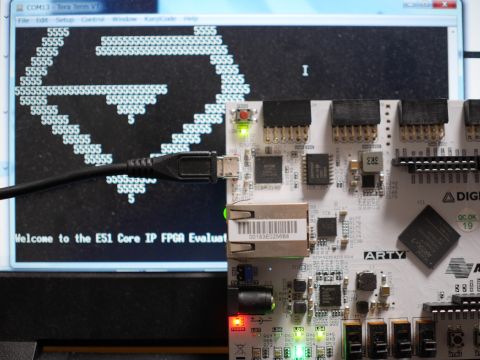

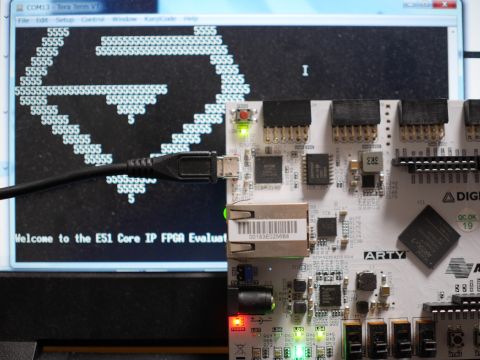

32bitコアのE20、E21、E31と、64bitコアのE51がありますが、今回は64bitコアの「SiFive E51 Standard Core FPGA Eval Kit」をダウンロードして書き込んでみました。

ダウンロードするにはSiFiveにユーザ登録(無料)する必要があります。

Artyへの導入手順はこちらに解説があります。

RISC-Vプラットフォーム Freedom E300 ArtyFPGA ボードの実験 – FPGA開発日記

SiFiveの64bit RISC-VコアE51をArty FPGAで動作させる – FPGA開発日記

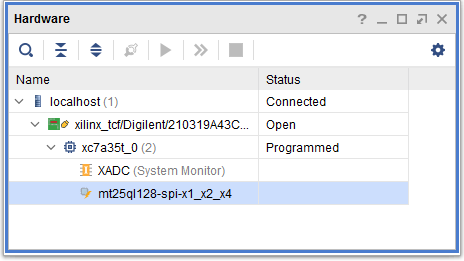

Vivado上でボードのメモリ設定を追加するという作業が必要ですが、この設定はボード上のメモリの種別に合わせる必要があります。

(2種類のうち、一方では「その種類のメモリはボード上に見つからない」というエラーが出ました)

追加できた設定は以下です。

書き込んだら、シリアルポートに起動メッセージが出せました。

この先へ進むには、RISC-VプロセッサをプログラムするためにJTAGインタフェースを接続する必要があります。

サンプルはARM-Tiny-USB-Hを使っていますが、手持ちのJ-Linkでも使えるっぽいです。

SiFive Arty FPGA Dev Kit – SEGGER – Support Wiki

そのためにはRISC-V用コンパイラとかも必要になりそうなので、とりあえず今日はここまでです。

コメント