それではRP2040のマニュアルを見ていきたいと思います。

全体的には5章の構成になっています。そのうち第1章がイントロダクション、第5章が電気的・機械的な仕様ですので、メインは2章から4章までになっています。

第2章がこのシステムをチップの全体の説明になっています。バスとかメモリマップ、DMA、CPUコア、ブートシーケンス、電源制御、リセット、クロック、GPIO等です。

続く第3章が、RP2040でも最も特徴的な「プログラマブルI/Oブロック」の解説です。

第4章は、おなじみのUART、I2C、SPI、PWM、タイマー、USB、ウォッチドッグ、リアルタイムクロック、ADコンバータなどで、あとSSI(Synchronous Serial Interface)という機能があります。

今回は第1章、第2章を見ていきます。

まず第1章。チップの仕様概略は前回触れましたので、省略します。

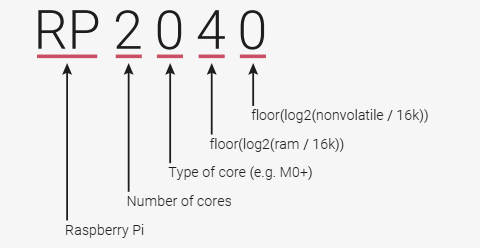

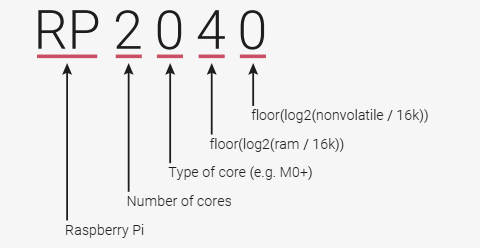

「RP2040」という型番について解説されていますので紹介しておきます。

RPは Raspberry Piですね。

2040の最初の2がCPUコア数。

2番目の0がプロセッサのタイプ。今回はCoretex-M0+なので0になっています。

続く4がRAM の容量を表しています。RAM の容量を16KBで割った値が、2の何乗になってるかで表します。RP2040は264KBですから、ほぼ256KB。16KBで割ると16、すなわち2の4乗ですので4という数字になります。

最後の0は不揮発性メモリの容量を、同じく容量16KBで割ったもののlog2ということで、RP2040は内蔵フラッシュはありませんので0になります。

将来的には、例えばCPUコアがCoretex-M4になってRP24シリーズになるとか、さらにSRAMを例えば512KB、フラッシュを2MBとした「RP2457」みたいなものも、もしかしたら出てくるかもしれませんね。

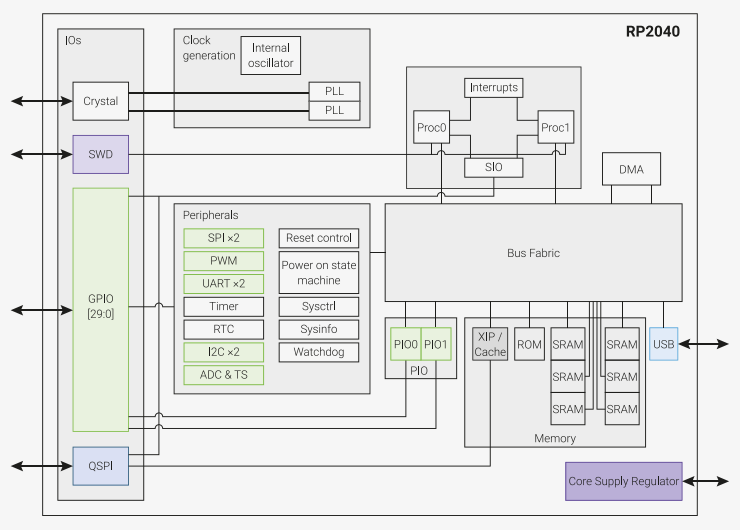

SoCとしてのRP2040の全体像がこちらになります。

目立つのはこの中央少し右下にある、PIOですね。PIO0とPIO1という二つのブロックに分かれています。

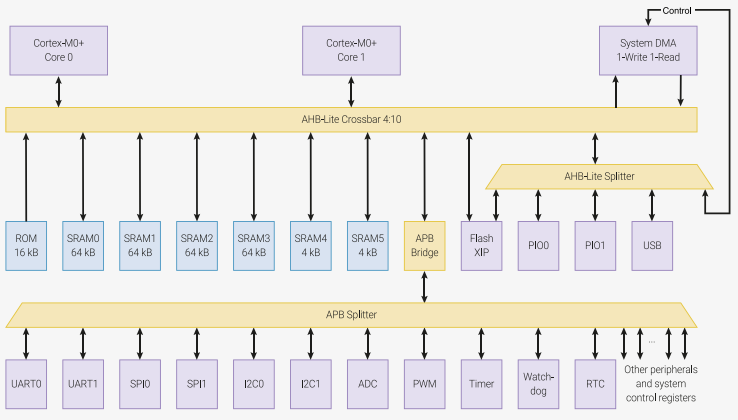

第2章は、まず内部バスの解説があります。

低速ペリフェラル専用のバスAPBと広帯域のバスAHB-Liteが搭載されています。

AHB-Liteは四つのマスター、プロセッサコア二つとDMAリードとDMAライト、に対して10個のダウンストリームとしてROM、SRAM×6ブロック、APBブリッジ、外付けフラッシュ、高速なペリフェラル(2つのPIOおよびUSB)が接続されます。

次にアドレスマップですが、概略は以下のようになっています。

0x00000000 ROM領域

0x10000000 外付フラッシュ領域

0x20000000 SRAM

0x40000000 APBペリフェラル

0x50000000 AHB-Liteペリフェラル

0xd0000000 I/Oポートレジスタ

0xe0000000 CPU コアの内部レジスタ

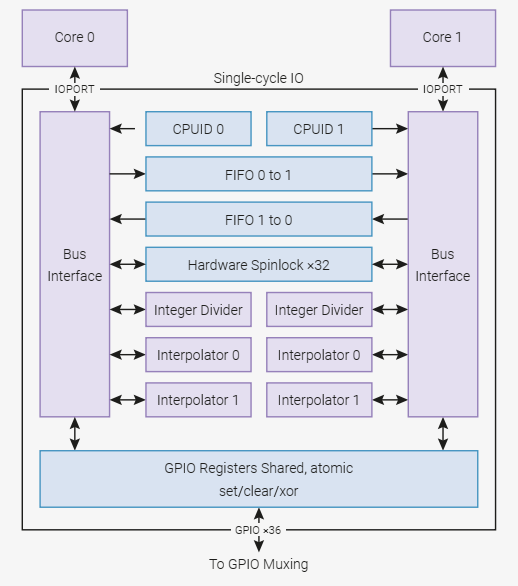

このI/Oポートレジスタですが、プロセッサから見るとメモリマップドI/Oになりますが、実際には直接バス上にあるわけではありません。CPUコアからはIOPORTという高速のポートを介して、シングルサイクルI/O(SCI)というブロックに繋がっています。

このSCIを介してGPIOと高速にやり取りすることができます。

SCIにはこのほか、整数の除算・数値の補間の計算・CPUコア間の通信をするmailboxインターフェースも含まれています。

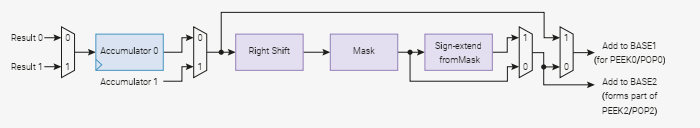

数値の補間を計算するInterpolatorというのは、音声や画像の処理に必要な繰り返しの演算処理をサポートするハードウェアのようです。加算とビットの右シフトとビットマスクと符合付き整数の処理が連結されています。

このハードウェア使って線形補間やアフィン変換などを行うサンプルが掲載されています。かなりいろいろなことができるようです。【→こちらの記事で解説】

これに続いてCPUコアやDMAコントローラ、割り込みについての解説があります。詳細は略しますが、DMAコントローラもなかなか多機能に見えます。

そのあとはメモリの解説になっています。ROMとSRAMの解説があり、ROMは16KBでブートコードが書き込まれています。SRAMは264KBですが、内訳は64KBのブロックが四つと4KBのブロックが二つになっています。4KBのブロックについては、二つのCPUコアそれぞれ1つ占有させてスタックや頻繁に使うコードを格納するために使うことも可能ですが、占有させてもアクセス速度的なメリットはないので264キロバイトのメモリーをリニアに使えばいい、というように記載されています。

これ以外に、フラッシュXIPのキャッシュとして16KB、USBのDPRAMに4KBのSRAMがあり、これらのデバイスを使わない場合にはこのSRAM領域も利用可能だそうです。

XIPはexecute-in-placeのことで、外付けフラッシュに入っている命令コードを一旦内蔵メモリの方に移して、それを実行する・・・という処理をしなくていい、フラッシュが最初からメモリーマップ上にあるように見えるという仕掛けです。

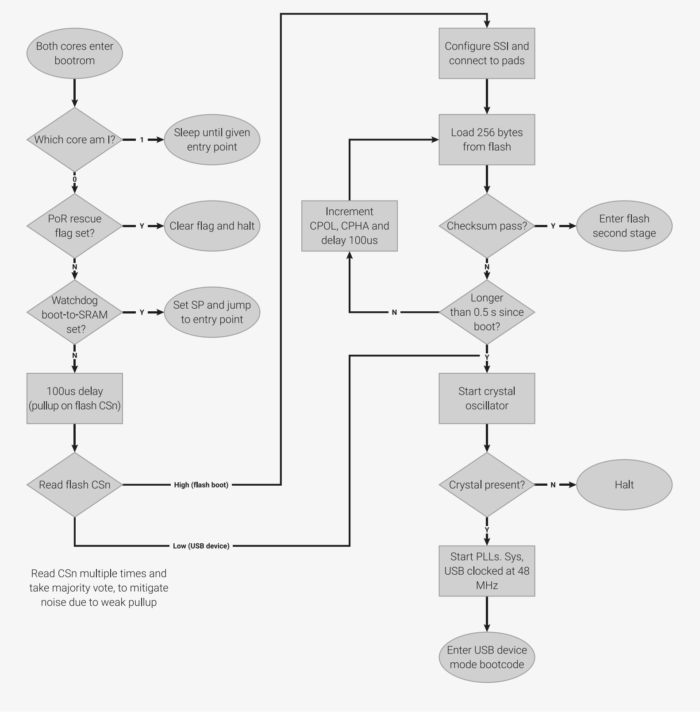

起動プロセスについても詳しく書かれています。前回も書きましたが、RP2040にはBOOTROM が入っていて、このROMのコードがUSBからフラッシュメモリに書き込むための仕組みを提供しています。そのコードもGithubで公開されています。

このBOOTROMを書き換えることはできませんが、そのコードには「ウォッチドッグレジスタに特定の値が書き込まれていると、外部の命令を実行する」という仕組みが組み込まれており、これを使って自分のコードを実行させることも可能なようです。この機能はデバッグに使うことができます。

BOOTROMに入っているコードの主な用途は、USB経由でファイルをドラッグ&ドロップするとフラッシュに書き込まれるという機能ですが、フラッシュの代わりにSRAMに書き込むこともできるようです。さらに、USBマスストレージクラスではなく、USB PICOBOOTというインターフェースも提供されており、これを使ってメモリの読み書きや命令の実行など、より柔軟な操作が行えるようです。

2章はこのあと、電源・リセット・クロック・オシレータ・PLLなども、詳細な解説がなされていますが省略します。

そのあとはGPIOの解説になっています。様々な機能を割り当てることができますので、その設定のためのレジスタの解説が表形式で延々と書かれていますが、見た感じ、他のMCUのGPIOと比べてあまり変わったことはなさそうです。

最後にシステム情報・システム設定情報の解説がついていますが、これも省略します。

印象的なのはInterpolatorですね。RP2040のプロセッサはM0+なので、命令セットは若干非力ですが、Interpolatorを使いこなすことで重たい処理もある程度こなせそうです。SDKには、Interpolatorを使ってオーディオ信号を処理するコードが含まれているそうです。

コメント